QuickLogic wins eFPGA IP contract for ASIC on Intel 18A process

Deal and technology

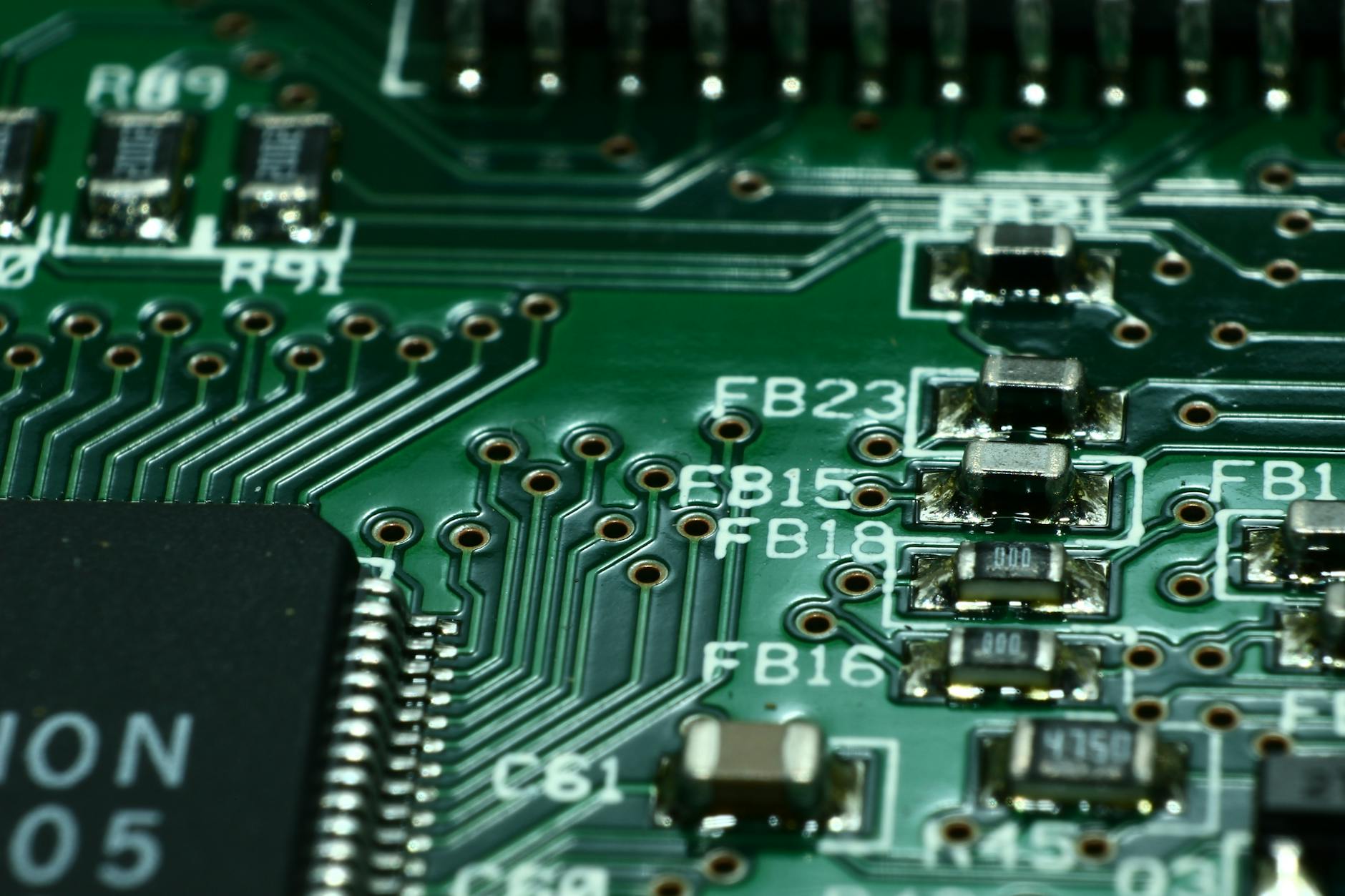

FPGA specialist QuickLogic announced on March 17 that it has secured a contract worth reportedly “several hundred thousand dollars” to supply hardened embedded FPGA (eFPGA) IP for a customer ASIC built on Intel’s 18A process. The company says the new generation of IP delivers improved PPA — power, performance and area — over prior products, positioning it for use in both ultra‑high‑density eFPGA cores inside ASICs and larger discrete FPGA devices.

QuickLogic said it works closely with key customers to identify and implement the design changes that matter. It has been reported that the PPA gains were developed under a 2025 contract framework and that the vendor expects the improvements, coupled with better cost sensitivity, to broaden the range of markets and applications it can address.

Why it matters

For Western readers unfamiliar with eFPGA: the technology lets chip designers add post‑manufacture reconfigurability to otherwise fixed ASICs and SoCs, reducing time‑to‑market and enabling flexible product updates. Who benefits? Telecom, AI accelerators and edge devices that need a balance of fixed silicon efficiency and field programmability.

This announcement also sits against a broader strategic backdrop. Advanced nodes and hardened IP at the leading edge are central to global chip competition and supply‑chain policy debates. While there is no allegation this specific deal touches export controls, developments that improve access to high‑density IP on advanced processes are notable given ongoing US‑China tensions over semiconductor technologies.

What to watch

Can QuickLogic turn this validation into repeatable, larger deals and gain share against bigger FPGA incumbents? The company argues yes, pointing to both its PPA gains and enhanced cost competitiveness. For the market, the question is whether hardened eFPGA IP at advanced nodes will become a mainstream way to harmonize ASIC efficiency with FPGA flexibility — and how that trend will interact with geopolitical pressure on advanced chip supplies.